Добрый день, уважаемые эксперты. Прежде чем использовать FIFO в проекте, решил написать для него простенький тест.

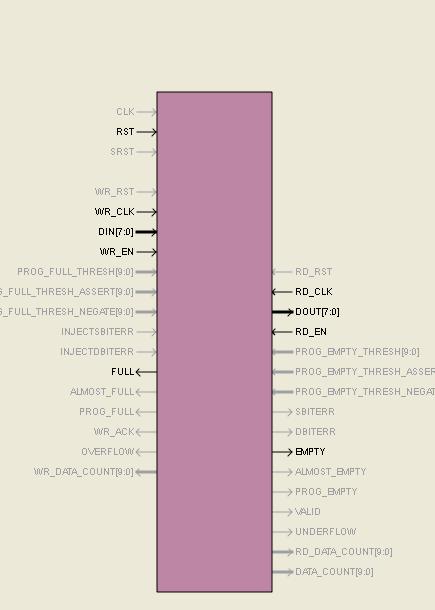

Итак, при помощи IP Core Generator получил FIFO следующего вида:

Код для тестирования:

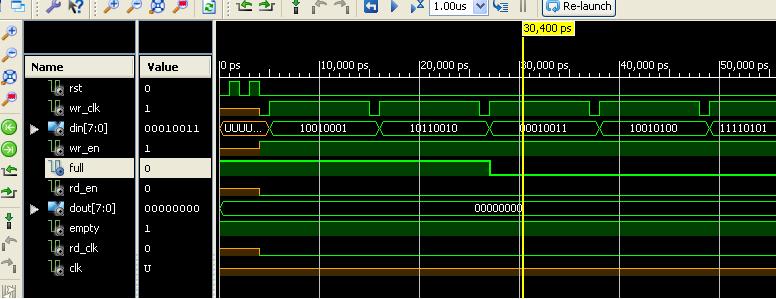

Симуляция на ISim дала следующие результаты:

То есть судя по полученным данным после сброса FIFO полное (full = '1'), затем, по переднему фронту третьего импульса записи (wr_clk) full сбрасывается в ноль. При этом флаг empty постоянно установлен в '1', даже когда full также равен единице. Догадываюсь, что должно быть совсем не так :-)

Я новичок в программировании ПЛИС. Подскажите, пожалуйста, в чем может быть ошибка?

Раздел: ПЛИС

Итак, при помощи IP Core Generator получил FIFO следующего вида:

Код для тестирования:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx primitives in this code.

library UNISIM;

use UNISIM.VComponents.all;

entity fifo_testbench is

end fifo_testbench;

architecture Behavioral of fifo_testbench is

component fifo_16x4

port(

rst: IN STD_LOGIC;

wr_clk: IN STD_LOGIC;

din: IN STD_LOGIC_VECTOR(7 DOWNTO 0);

wr_en: IN STD_LOGIC;

full: OUT STD_LOGIC;

rd_en: IN STD_LOGIC;

dout: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

empty: OUT STD_LOGIC;

rd_clk: IN STD_LOGIC

);

end component;

signal rst: STD_LOGIC;

signal wr_clk: STD_LOGIC;

signal din: STD_LOGIC_VECTOR(7 DOWNTO 0);

signal wr_en: STD_LOGIC;

signal full: STD_LOGIC;

signal rd_en: STD_LOGIC;

signal dout: STD_LOGIC_VECTOR(7 DOWNTO 0);

signal empty: STD_LOGIC;

signal rd_clk: STD_LOGIC;

signal clk: STD_LOGIC;

begin

FIFO_INIT: fifo_16x4 port map(

rst => rst,

wr_clk => wr_clk,

din => din,

wr_en => wr_en,

full => full,

rd_en => rd_en,

dout => dout,

empty => empty,

rd_clk => rd_clk);

FIFO_TEST: process

begin

-- сброс FIFO

rst <= '0'; wait for 1 ns; rst <= '1'; wait for 1 ns;

-- заполняем FIFO

rst <= '0'; rd_clk <= '0'; rd_en <= '0'; wr_en <= '1';

wr_clk <= '0'; wait for 1 ns;

wr_clk <= '1'; din <= "10010001"; wait for 10 ns;

wr_clk <= '0'; wait for 1 ns;

wr_clk <= '1'; din <= "10110010"; wait for 10 ns;

wr_clk <= '0'; wait for 1 ns;

wr_clk <= '1'; din <= "00010011"; wait for 10 ns;

wr_clk <= '0'; wait for 1 ns;

wr_clk <= '1'; din <= "10010100"; wait for 10 ns;

wr_clk <= '0'; wait for 1 ns;

wr_clk <= '1'; din <= "11110101"; wait for 10 ns;

wr_clk <= '0'; wait for 1 ns;

wr_clk <= '1'; din <= "10010110"; wait for 10 ns;

wr_clk <= '0'; wait for 1 ns;

-- читаем из FIFO

rd_en <= '1';

rd_clk <= '1'; wait for 10 ns;

rd_clk <= '0'; wait for 1 ns;

rd_clk <= '1'; wait for 10 ns;

rd_clk <= '0'; wait for 1 ns;

rd_clk <= '1'; wait for 10 ns;

rd_clk <= '0'; wait for 1 ns;

rd_clk <= '1'; wait for 10 ns;

rd_clk <= '0'; wait for 1 ns;

rd_clk <= '1'; wait for 10 ns;

rd_clk <= '0'; wait for 1 ns;

rd_clk <= '1'; wait for 10 ns;

rd_clk <= '0'; wait for 1 ns;

rd_clk <= '1'; wait for 10 ns;

rd_clk <= '0'; wait for 1 ns;

rd_clk <= '1'; wait for 10 ns;

rd_clk <= '0'; wait for 1 ns;

end process;

end Behavioral;

Симуляция на ISim дала следующие результаты:

То есть судя по полученным данным после сброса FIFO полное (full = '1'), затем, по переднему фронту третьего импульса записи (wr_clk) full сбрасывается в ноль. При этом флаг empty постоянно установлен в '1', даже когда full также равен единице. Догадываюсь, что должно быть совсем не так :-)

Я новичок в программировании ПЛИС. Подскажите, пожалуйста, в чем может быть ошибка?

Раздел: ПЛИС